## TWO BOUNDARY BASED DISPATCHING RULE FOR ON-TIME DELIVERY AND THROUGHPUT OF WAFER FABS WITH DEDICATION CONSTRAINTS

Kang H. Cho Yong H. Chung You I. Choung Sang C. Park

Byung H. Kim

Dept. of Industrial Engineering Ajou University. Woncheon, Suwon, KOREA VMS Solutions Co., Ltd. Hanshin S-MECA 611, Gwanpyeong, Yuseong-gu Daejeon, 305-509, KOREA

# ABSTRACT

Presented in this paper is a dispatching rule to achieve the on-time delivery and throughput for a semiconductor wafer fabrication (FAB) with dedication constraint. It is necessary to improve throughput of production system as well as on-time delivery to make semiconductor companies more competitive. To be successful in the globalized competition, most of the companies have applied a concept of the production target which is defined as the quantity of production to be achieved for each day. Also, it is necessary to consider natural bias that significantly affects the alignment of patterns between different photolithography steps. As the natural bias has a negative effect on the quality and yield of products, most manufacturers have applied dedication constraint. If the dedication constraint is no managed properly, it may decrease the utilization of the photo machines related to the performance of wafer FAB.

To overcome the problem, we propose the two boundary based dispatching rule considering the dedication constraint. The simulation model based on MIMAC6 was developed to prove the performance of this proposed dispatching rule, and conducted a simulation by using MOZART<sup>®</sup>. The simulation results clearly show the advantages of the proposed dispatching rule over the other dispatching rules.

# **1 INTRODUCTION**

Semiconductor wafer fabrication (FAB) is one of the most complex manufacturing processes in the world, because of its the reentrant processing flow, random yields and rework, complex product flows, timecritical operations, rapidly changing products and technologies (Jerald et al. 2002; Lawrence et al. 1988). As a result, it is difficult to manually control and manage semiconductor wafer FAB in an optimum manner (Subhash and Sameer 2001; Lee 2001). To be successful in the globalized competition, semiconductor manufacturers have to offer high-quality, high amount of production, on-time delivery to their customers. To maximize these objectives, the most semiconductor manufacturers have applied the concept of production target which is the amount of production to certainly be achieved for each day. As determine the production target, it can be estimated using the wafer due date information of orders based on backward planning, i.e. delivery date promised of products (Lee et al. 2008).

To improve the performance of wafer FAB, the dispatching decision is very important because it could significantly affect the result of on-time delivery and throughput. Thus, dispatching decisions for wafer FAB have been studied extensively in the literature. Most studies have aimed to develop dispatching rules to reduce cycle time and increase throughput (Lu et al. 1994; Li et al. 1996; Yoon and Lee 2000). Some have intended to reduce the tardiness (Lu and Kumar 1991; Kim et al. 2001), while others have aimed to improve on-time delivery, in addition to an improvement in cycle time and

throughput (Kim et al. 1998; Lee et al. 2002; Dabbas and Fowler 2003). Yet most previous studies have assumed that there is no dedication constraint for a photolithography (photo) machine.

In modern FAB, semiconductor manufacturing processes consist of hundreds of steps such as etching, diffusion, ion implantation, and photo. Among these various steps, the photo step is usually considered as the bottleneck step because of the expensive photo machine (Chung et al. 2016). Therefore, the performance of photo machines determines the performance of a FAB related to on-time delivery and throughput, and thus it is necessary to maintain full utilization of photo machines (Sha et al. 2006). To Maximize the utilization of photo machines, it is necessary to consider natural bias that significantly affects the alignment of patterns between different photo steps (Pham, H. N. A. et al. 2008). The natural bias has a negative effect on the quality and yield of products. Most manufacturers have applied dedication constraint to overcome this problem. If the constraint is not managed properly, it may decrease the utilization of the photo machines.

As dedication constraint is strongly related to the utilization of a photo machines, various studies have been conducted on wafer FAB scheduling with dedication constraint. These studies can be classified by two approaches to achieve high utilization of photo machines (Chung et al. 2016). Studies belong to the first approach were focused on assigning of each lot for photo machines at the first photo step. Kidambi developed a methodology based on the combination of earliest start date rule and least lots ahead rule to allocate lots in the first photo step. (Kidambi 2001). Shr et al. proposed a heuristic scheduling approach for achieving load balancing among identical photo machines (Shr et al. 2006; Shr et al. 2008). Pham et al. presented an integer linear program based framework to solve lot assignment problems with respect to dedication constraint (Pham et al. 2008). Klemmt and Weigert proposed a simulation based optimization approach for parallel machine problems with dedication constraint (Klemmt and Weigert 2011). But, other studies were focused on controlling the flow of dedicated lots regarding the second approach. Wu et al, introduced a different approach to prevent the problems that may be caused by dedication constraint. They developed a release policy and dispatching rules to prevent load unbalance in conjunction with work-in-process (WIP) starvation of photo machines with dedication constraint (Wu et al. 2006; Wu et al. 2008(a): Wu et al. 2008(b)). Although there have been various studies on the subject of dedication constraint, the FAB still has significant challenges in achieving high utilization of photo machines.

Although it is possible to produce wafer lots as much as the production target, it may cause a tardiness of wafer lots unless dedication constraint of photo machines is not managed properly. Most of previous studies have been designed to achieve maximal productivity, rather than to assign the appropriate wafer lots to be processed with dedication constraint.

This research focuses on both the first approach regarding assignment of lots and second approach regarding controlling the flow of dedicated lots considering the production target. To assign the appropriate wafer lots, we use a concept of dedication load, which is defined as the sum of the workload for lots dedicated to each photo machine (Chung et al. 2016). To control the flow of dedicated lots, we estimate the achievement rate of production target, which is defined as how much wafer lots are produced against production target for each step. By using the dedication load and the production target, we proposes a dispatching rule to improve on-time delivery rate and throughput with dedication constraint.

To perform the simulation, the commercial software MOZART<sup>®</sup> developed by VMS solutions was employed. The remainder of this paper is organized as follows. Section 2 provides a detailed explanation for two boundary dispatching rule. The experimental results for proposed dispatching rule are analyzed in Section 3. Finally, concluding remarks are presented in Section 4.

### 2 TWO BOUNDARY BASED DISPATCHING RULE

This section explains the two boundary based dispatching rule that is designed to maximize the on-time delivery and throughput for products in wafer FAB. We refer the interested reader to (Chung et al. 2016) for details. Considering a concept of dedication load in that research attribute gives rise to the possibility of increasing the utilization of the photo machines. As mentioned above, high utilization of photo

machines has a positive effect on the performance of wafer FAB such as on-time delivery and throughput. Therefore, this paper develops a method that adapts a concept of dedication load to deal with work load balance of identical photo machines for maintaining the high utilization.

To apply the dedication load to proposed dispatching rule, we noticed that photo steps can be classified into two types: 1) dedication mark step and 2) dedication step. Dedication mark step includes only the first photo step of each process. The dedication step includes all photo steps except for the first photo step. We can calculate the dedication load for each photo machine to determining type of photo step (dedication mark step or dedication step) where a lot will be processed.

To satisfying the requirement of customers, it is necessary to improve the productivity and on-time delivery. This paper suggests calculating the achievement rate of production target for each product in order to control the flow of dedicated lots, whenever a machine becomes available. The achievement rate of production target indicates how much wafer lots are produced against production target for each step.

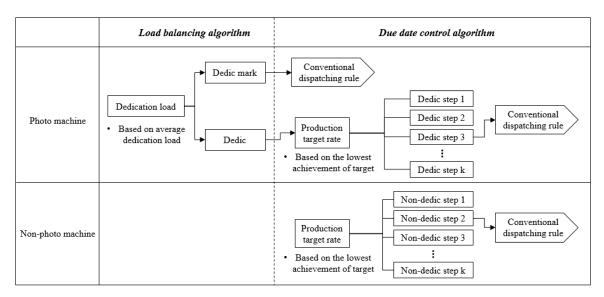

Figure 1: Overview of the proposed dispatching rule.

The main algorithm is presented first, and additional explanations are then provided. As shown in Figure 1, the main algorithm consists of three main stages. 1) determine a type of photo step based on dedication load, 2) determine a step having the lowest achievement of production target, 3) determination of lot to be processed next based on conventional dispatching rule. Although there are three main stages, this paper focuses on the first two stages. Before explaining the proposed dispatching rule, it is necessary to define several terms as follows.

- $M_k$ : k<sup>th</sup> photo machine.

- M<sub>d</sub>: a photo machine that becomes available at current time.

- D-lots<sub>k</sub>: lots available for dispatching of  $M_k$  at current time.

- Workload(i, M<sub>k</sub>): the workload of M<sub>k</sub> for lot i at current time.

- $DL_k$ : the dedication load of  $M_K$  at current time.

For the *Load balance algorithm*, an algorithm was used to determine the type of photo step to process calculating the dedication load of photo machines. To calculate the dedication and determine the type of photo step, we used an algorithm in the previous research as follows.

#### ■ Load balance algorithm:

$\begin{array}{ll} \mbox{Step 1}) \ DL_{avg} = \mbox{calculate the average of dedication loads for identical photo machines;} \\ \mbox{Step 2}) \ If(DL_d < DL_{avg}) \\ & \mbox{dedicType} = \mbox{dedication mark type;} \\ \mbox{Else} \\ & \mbox{dedicType} = \mbox{dedication type;} \\ \mbox{Step 3}) \ \mbox{corr-lots} = \mbox{find lots at steps corresponding to dedicType;} \\ \mbox{Step 4}) \ If(\mbox{corr-lots is null}) \\ & \mbox{return D-lots}_k; \\ \mbox{Else} \\ & \mbox{Return corr-lots;} \end{array}$

If the dedication load of photo machines is not managed properly, it may cause load unbalance of the photo machines. To manage balancing of workload of the photo machines, it is important to control the dedication load of photo machines similar to the average dedication loads for identical photo machines. If  $DL_d$  was lower than  $DL_{avg}$ , the dispatching rule has to return lots at the dedication mark step. Because dedication load of a photo machine increases in when it processes a lot at the dedication mark step. On the contrary, lots are returned at the dedication step when  $DL_d$  was higher than  $DL_{avg}$ . Determining the type of photo step, the dedication loads of all photo machines are managed properly to avoid idle of the photo machines. As the *Load balance algorithm* determined the type of photo steps without considering lots for dispatching, it was necessary to check whether there existed a lot that could be processed. If there are no any lots determined the algorithm at the dedication mark step, then it is necessary to select lots at the dedication steps to prevent from idle of the photo machines. For the *Due date control algorithm*, we define several terms as follows:

- Step<sub>i</sub>:  $j^{th}$  step corresponding to lots available for dispatching except for dedication mark step

- Actual<sub>i</sub>: the throughput of step<sub>i</sub> until current time.

- Target<sub>i</sub>: the production target during a day at step<sub>i</sub>

### **Due date control algorithm:**

Step 1)  $AR_i$  = calculate the achievement rate of production target for each step;

$$AR_j = \frac{Actual_j}{Target_j};$$

Step 2) L-step<sub>j</sub> = find step corresponding to the lowest achievement rate among AR<sub>j</sub>;

Step 3) corr-lots = find lots corresponding to L-step<sub>j</sub>;

Step 4) Return corr-lots;

In the second stage, the *Due date control algorithm* used an dispatching rule to determine a step estimated the lowest achievement of production target. First, it is necessary to calculate the production target for the products. Production target means the amount of production to be achieved for each day. We use pegging to calculate the production target. Pegging is defined as the process of assigning wafer lots to orders, and it is very essential to meet customers' demands in terms of throughput and due dates in a wafer FAB. It determines the production target for each step. When a machine (photo machine or non-photo machine) becomes available to dispatch a new lot, the algorithm calculate the achievement rate of production target for each lot at all steps determined by previous stage. Among these steps, the algorithm determines a step in which the achievement rate of production target is the lowest. Assuming the

algorithm considered the lowest rate, this means that it forced lots which has to be produced to processed next. If the achievement of production rate is tie, the lots corresponding to steps is determined next stage.

In the final stage, it is essential to determine a lot to be processed next based on the lots determined in the previous stage. To determine a lot to be processed next, we employed a conventional dispatching rule that considered the required objective as mentioned above. In this paper, proposed dispatching rule apply the operation due date (ODD) dispatching rule to achieve on-time delivery and throughput.

### **3 EXPERIMENTAL RESULTS**

To conduct the simulation experimentation, we employed the wafer FAB dataset MIMAC6 from Measurement and Improvement of Manufacturing Capacities (MIMAC) (Fowler and Robinson 1995). As a reference model, we modified the MIMAC dataset to construct a modern FAB model. Because the MIMAC dataset was developed a few decades ago, it is necessary to consider capacity, type of machines and quantity demand as a common example such as dedication constraint.

In this paper, we employ the MOZART<sup>®</sup> engine developed by VMS solutions (Ko et al. 2013). Based on master plan (MP) and current WIP, MOZART<sup>®</sup> generates loading schedule of each tool and production plan using dispatching rule required objectives. To compare the performance of the proposed dispatching rule, it is necessary to design simulation experiments by using the ODD dispatching rule. ODD is calculated in the following way : ODD = Due Date - Remaining RPT \* Flow factor where RPT is the raw processing time of the lot. Flow factor is defined as the target cycle times divided by the RPT. For the objective of this paper, it is necessary to apply the ODD dispatching rule because the objective of this dispatching rule is to achieve the on-time delivery.

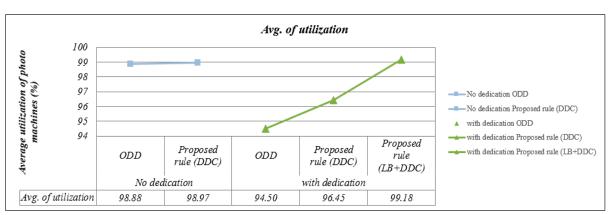

As performance measures to estimate dispatching rule, the flow factor for production lots is determined as 1.39. Although a low flow factor makes little or no variation in equipment availability, it can show the problem caused by dedication. The FAB model was simulated for six months except for first four months because this period represented the warm-up period. To show the effectiveness of the proposed dispatching rule, we took into account percentage of on-time delivery rate, throughput, variance utilization of photo machines, and average utilization of photo machines. For convenience, if *Due date control algorithm* is applied to the proposed dispatching rule, we refer to it as 'Proposed rule (DDC)'. The same is true for the case of *Load balance algorithm* (LB).

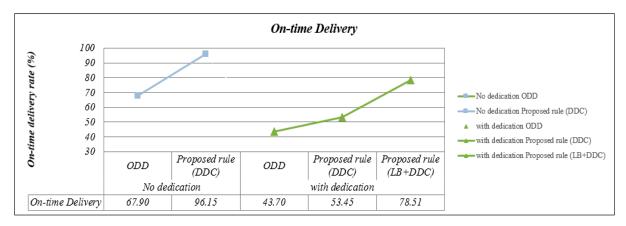

Figure 2: Percentage of on-time delivery.

Cho, Chung, Chung, Kim, and Park

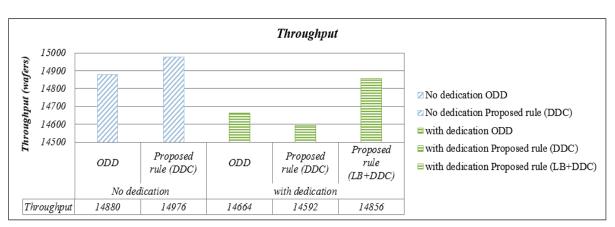

Figure 3: Amount of throughput.

Figure 2, 3, 4 and 5 shows the performance measures for the objectives of proposed dispatching rule. The results provide the effectiveness of the dedication constraint and it was applied to only first two dispatching rules. When the simulation was conducted with no dedication constraint, the proposed dispatching rule show that on-time delivery rate and throughput also are improved except for variance and average of photo machines utilization. This results indicate that there is a no difference in the performance of photo machines without dedication constraint between the two cases ODD and Proposed rule (DDC). It could identify the problem of photo machines caused by dedication constraint.

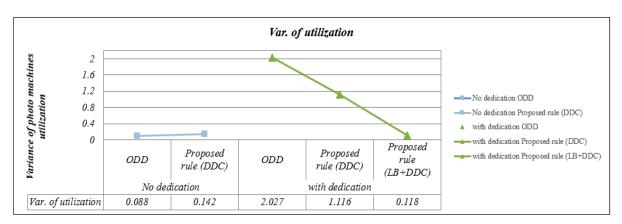

Figure 4: Variance of photo machine utilization.

Cho, Chung, Chung, Kim, and Park

Figure 5: Average of photo machine utilization.

Under the dedication constraint, Figure 4 and 5 shows that the proposed dispatching rule was superior to the other dispatching rules with respect to the load balancing of photo machines. The results indicated it was important to achieve the production target for high performance of the FAB. Additionally, with dedication constraint, it also was important to achieve the load balance for the photo machines. As the load balance is improve, on-time delivery and throughput also are improved in the all results. Moreover, the proposed dispatching rule guarantees the maximum on-time delivery, throughput, load balance of photo machines and utilization of photo machines.

# 4 SUMMARY

To survive in the modern wafer FAB, it is important to manage the complex manufacturing processes to be appropriately scheduled to make semiconductor companies more competitive. To be successful in the globalized competition, it is necessary to improve throughput of production system as well as on-time delivery. To maximize these objectives, the most semiconductor manufacturers have applied the concept of production target which is the quantity of production to be achieved for each day, it can be estimated using the wafer due date information of orders based on backward planning. Most of FABs have natural bias that significantly affects the quality of products caused by the alignment of patterns between different photo machines. The natural bias has a negative effect on the yield of products, also.

In this paper, we proposed the two boundary based dispatching rule for on-time delivery rate and throughput in wafer FAB with dedication constraint. To simulate the proposed dispatching rule, we used the commercial software MOZART<sup>®</sup> developed by VMS solutions and the FAB model constructed by using MIMAC dataset 6. The FAB model was modified to reflect the nature of the real modern FAB. Simulation results showed clear advantages of the proposed dispatching rule over the other dispatching rules, and that it is important to identify an appropriate dedication machine for products.

# ACKNOWLEDGMENTS

This work was partially supported by Defense Acquisition Program Administration and Agency for Defense Development (UD150042AD, UD1600BD); ICT R&D program of MSIP/IITP (R-20150505-000691); National Research Foundation (NRF-2015R1A2A2A01005871) by the Ministry of Education, Science and Technology, Korea; and a grant (17CTAP-C129828-01) from the Infrastructure and Transportation Technology Promotion research program funded by the Ministry of Land, Infrastructure and Transport of the Korean government.

### REFERENCES

- Akcalt, E., K. Nemoto, and R. Uzsoy. 2001. "Cycle-time Improvements for Photolithography Process in Semiconductor Manufacturing." *IEEE Transactions on Semiconductor Manufacturing* 14:48-56.

- Andreas, K., and W. Gerald. 2011. "An Optimization Approach for Parallel Machine Problems with Dedication Constraints: Combining Simulation and Capacity Planning." In *Proceedings of the 2011 Winter Simulation Conference*, edited by S. Jain, R. R. Creasey, J. Himmelspach, K. P. White, and M. Fu, 1986-1998. Piscataway, New Jersey: Institute of Electrical and Electronics Engineers, Inc.

- Chung, Y. H., K. H. Cho, B. H. Kim, and S. C. Park. 2016. "Dedication Load based Dispatching Rule for Photolithography Machines with Dedication Constraint." In *Proceedings of the 2016 Winter Simulation Conference*, edited by T. M. K. Roeder, P. I. Frazier, R. Szechtman, E. Zhou, T. Huschka, and S. E. Chick, 2731-2739. Piscataway, New Jersey: Institute of Electrical and Electronics Engineers, Inc.

- Dabbas, R. M. and J. W. Fowler. 2003. "A New Scheduling Approach Using Combined Dispatching Criteria in Wafer Fabs." *IEEE Transactions on Semiconductor Manufacturing* 16:501-510.

- Fowler, J., and J. Robinson. 1995. "Measurement and Improvement of Manufacturing Capacities (MIMAC): Final Report." *Technical Report 95062861A-TR*, SEMATECH, Austin, TX.

- Hiroyasu, T., I. Hiroaki, H. Hirotaka, and C. Takayuki. 2005. "Dynamic Load Balancing Among Multiple Fabrication Lines Through Estimation of Minimum Inter-Operation Time." *IEEE Transactions on Semiconductor Manufacturing* 18(1):202-213.

- Huy, N. A., A. M. D. Shr, H. N. A. Pham, and P. P. Chen. 2008. "An Integer Linear Programming Approach for Dedicated Machine Constraint." In *Proceedings of the Seventh IEEE/ACIS International Conference on Computer and Information Science*, 69-74.

- Jerald, H., D. Delp, D. Collins, and J. Si. 2002. "Understanding a Semiconductor Process using a Full-Scale Model." *IEEE Transactions on Semiconductor Manufacturing* 15(2):285-289.

- Johri, P. K. 1993. "Practical Issues in Scheduling and Dispatching in Semiconductor Wafer Fabrication." Journal of Manufacturing Systems 12:474-483.

- Kidambi, M. R. 2001. "Impact of Lot Dedication on the Performance of the FAB." Master. Thesis, Department of Industrial and Systems Engineering, Virginia Polytechnic Institute and State University, Blacksburg, Virginia.

- Kim, Y. D., J. G. Kim, B. Choi, and H. U. Kim. 2001. "Production Scheduling in a Semiconductor Wafer Fabrication Facility Producing Multiple Product Types with Distinct Due Dates." *IEEE Transactions* on Robotics and Automation 17:589-598.

- Kim, Y. D., J. U. Kim, S. K. Lim, and H. B. Jun. 1998. "Due-Date Based Scheduling and Control Policies in a Multiproduct Semiconductor Wafer Fabrication Facility." *IEEE Transactions on Semiconductor Manufacturing* 11(1):155-164.

- Ko, K., B. H. Kim, and S. K. Yoo. 2013. "Simulation Based Planning & Scheduling System: MOZART®." In *Proceedings of the Winter Simulation Conference*, edited by R. Pasupathy, S.-H. Kim, A. Tolk, R. Hill, and M. E. Kuhl, 4103-4104. Piscataway, New Jersey: Institute of Electrical and Electronics Engineers, Inc.

- Lawrence, M. Wein. 1988. "Scheduling Semiconductor Wafer Fabrication." *IEEE Transactions on Semiconductor Manufacturing* 1(3):115-130.

- Lee, B., Y. H. Lee, T. Yang, and J. Ignisio. 2008. "A Due-date based Production Control Policy using WIP Balance for Implementation in Semiconductor Fabrications." *International Journal of Production Research* 46(20):5515-5529.

- Lee, H. L. 2001. "Dispatching Heuristic for Wafer Fabrication" In *Proceedings of the 2001 Winter Simulation Conference*, 1215-1219. Computer Society, Washington, D.C..

- Lee, Y. H., J. Park, and S. Kim. 2002. "Experimental Study on Input and Bottleneck Scheduling for a Semiconductor Fabrication Line." *IIE Transactions* 34:179-190.

- Li, S., T. Tang, and D. W. Collins. 1996. "Minimum Inventory Variability Schedule with Applications in Semiconductor Fabrication" *IEEE Transactions on Semiconductor Manufacturing* 9:145-149.

- Lin, J. T., F. K. Wang, and P. C. Kuo. 2005. "A Parameterized-Dispatching Rule for a Logic IC Sort in a Wafer Fabrication." *Production Planning & Control* 16(5):426-436.

- Liu, A., A. M. D. Shr, and Y. Cheng. 2006. "A Fuzzy Scheduling System for Dedicated Machine Constraint." In Proceedings of the 2006 Joint Conference on Information Sciences, Kaohsiung, Taiwan.

- Lu, S. C. H., D. Ramaswamy, and P. R. Kumar. 1994. "Efficient Scheduling Policies to Reduce Mean and Variance of Cycle-time in Semiconductor Manufacturing Plants." *IEEE Transactions on Semiconductor Manufacturing* 7:374-388.

- Lu, S. H. and P. R. Kumar. 1991. "Distributed Scheduling based on Due Dates and Buffer Priorities." *IEEE Transactions on Automatic Control* 36:1406-1416.

- Miwa, T., N. Nishihara, and K. Yamamoto. 2005. "Automated Stepper Load Balance Allocation System." *IEEE Transactions on Semiconductor Manufacturing* 18(4):510-516.

- Mönch. L., M. Prause, and V. Schmalfuss. 2001. "Simulation-Based Solution of Load-Balancing Problems in the Photolithography Area of a Semiconductor Wafer Fabrication Facility." In *Proceedings of the 2001 Winter Simulation Conference*, 1170-1177. Piscataway, New Jersey: Institute of Electrical and Electronics Engineers, Inc.

- Park, S. C., E. Ahn, Y. Chung, K. Yang, B. H. Kim, and J. C. Seo. 2013. "Fab Simulation with Recipe Arrangement of Tools." In *Proceedings of the 2013 Winter Simulation Conference*, edited by R. Pasupathy, S. H. Kim, A. Tolk, R. Hill, and M. E. Kuhl, 3840-3849. Piscataway, New Jersey: Institute of Electrical and Electronics Engineers, Inc.

- Pham, H. N. A., A. M. D. Shr, and P. P. Chen. 2008. "An Integer Linear Programming Approach for Dedicated Machine Constraint." *International Conference on Computer and Information Science*, Washington DC, 69-74.

- Sha, D. T., S. Y. Hsu, Z. H. Che, and C. H. Chen. 2006. "A Dispatching Rule for Photolithography Scheduling with an On-Line Rework Strategy." *Computers & Industrial Engineering* 50:233-247.

- Shirley, J. T. 2011. "Bottleneck Management Strategies in Semiconductor Wafer Fabrication Facilities." In Proceedings of the 2011 International Conference on Industrial Engineering and Operations Management, 3-8. Kuala Lumpur, Malaysia.

- Shr, A. M. D., A. Liu, and P. P. Chen. 2006. "A Heuristic Load Balancing Scheduling Approach for Dedicated Machine Constraint." In *Proceedings of the 19th International Conference on Industrial, Engineering & Other Applications of Applied Intelligent Systems(IEA/AIE'06)*, edited by M. Ali and R. Dapoigny, 750-759. Lecture Notes in Artificial Intelligence (LNAI) 4031, Springer-Verlag, Berlin Heidelberg.

- Shr, A. M. D., A. Liu, and P. P. Chen. 2006. "A Load Balancing Scheduling Approach for Dedicated Machine Constraint." In Proceedings of the 8th International Conference on Enterprise Information Systems ICEIS 2006, 170-175. Paphos, Cyprus.

- Shr, A. M. D., A. Liu, and P. P. Chen. 2006. "A Load Balancing Method for Dedicated Photolithography Machine Constraint." *Information Technology for Balanced Manufacturing Systems* 220:339-348.

- Shr, A. M. D., A. Liu, and P. P. Chen. 2008. "Load Balancing Among Photolithography Machines in the Semiconductor Manufacturing System." *Journal of Information Science and Engineering* 24:379-391.

- Subhash C. S., Sameer T. S. 2001. "Reduction of Average Cycle Time at a Wafer Fabrication Facility." *Technical Report,* Virginia Tech, Blacksburg, VA.

- Uzsoy R., L. K. Church, and I. M. Ovacik. 1992. "Dispatching Rules for Semiconductor Testing Operations: a Computational Study." In *Proceedings of the thirteenth IEEE/CHMT international electronics manufacturing technology symposium*, 272-276.

- Wu, M. C., Y. L. Huang, Y. C. Chang, and K. F. Yang. 2006. "Dispatching in Semiconductor FABs with Dedication Features." *International Journal of Advanced Manufacturing Technology* 28:978-984.

- Wu, M. C., S. Chiou, and C. Chen. 2008. "Dispatching for Make-to-order Wafer Fabs with Dedication and Mask Set-up Characteristics." *International Journal of Production Research* 46:3993-4009.

- Wu, M. C., J. Jiang, and W. Chang. 2008. "Scheduling a Hybrid MTO/MTS Semiconductor Fab with Dedication Features." *International Journal of Production Economics* 112:416-426.

- Yang, J. H. 2015. "Minimizing Total Completion Time in a Two-stage Hybrid Flow Shop with Dedicated Machines at the First Stage." *Computers and Operations Research* 58:1-8.

- Yoon, H. J. and D. Y. Lee. 2000. "A Control Method to Reduce Standard Deviation of Flow Time in Wafer Fabrication." *IEEE Transactions on Semiconductor Manufacturing* 13:389-392.

# **AUTHOR BIOGRAPHIES**

**KANG H. CHO** received a bachelor degree (2013) in industrial and information system engineering and a master degree (2015) in industrial engineering, Ajou University, Korea. He is now a Ph. D candidate in industrial engineering, Ajou University, Korea. He is interested in simulation-based scheduling and planning, virtual manufacturing, and image pattern recognition. His email address is sung15jin@ajou.ac.kr.

**YONG H. CHUNG** received a bachelor degree (2011) in industrial and information system engineering and a master degree (2013) in industrial engineering, Ajou University, Korea. He is now a Ph. D candidate in industrial engineering, Ajou University, Korea. He is interested in simulation-based scheduling and planning, digital manufacturing, and mesh simplification. His email address is yongho1230@gmail.com.

**YOU I. CHOUNG** is a researcher in the Research Center of Engineering, Ajou University, Korea. Before joining Ajou University, he was a principal engineer for semiconductor manufacturing of Samsung Electronics. He received a BS from Sungkyunkwan University in 1991, a MS from KAIST in 1994, and a Ph.D. from KAIST in 1999, all in Industrial Engineering. His main interests are Supply Chain Management, scheduling, simulation, and system engineering on semiconductor manufacturing. His email address is youinchoung@gmail.com.

**BYUNG H. KIM** is the president of VMS Solutions Co., Ltd. since 2000. He received a BS from Sungkyunkwan University in 1993, a MS from KAIST in 1995, and a Ph.D. from KAIST in 2001, all in Industrial Engineering. His main interests are simulation-based scheduling and planning, manufacturing information systems, BPMS, and virtual manufacturing. His email address is kbhee@vms-solutions.com.

**SANG C. PARK** was granted his bachelor (1994), master (1996) and Ph.D. (2000) degrees in industrial engineering, Korea Advanced Institute of Science and Technology (KAIST). He is a professor in Dept. of IE, Ajou University, Korea, since 2004. He is interested in modeling and simulation (M&S), combat simulation for defense, and digital manufacturing system. His email address is scpark@ajou.ac.kr.